| Sign In | Join Free | My ecer.jp |

|

- Home

- Products

- About Us

- Quality Control

- Contact Us

- Get Quotations

| Sign In | Join Free | My ecer.jp |

|

Brand Name : Anterwell

Model Number : 74HC585D

Certification : Original Factory Pack

Place of Origin : Thailand

MOQ : 5pcs

Price : Negotiation

Payment Terms : T/T, Western Union,PayPal

Supply Ability : 2200PCS

Delivery Time : 1 Day

Packaging Details : please contact me for details

FEATURES : Output capability: standard

FEATURES2 : ICC category: SSI

Shipment : DHL, Fedex, TNT, EMS etc

Main Line : Ic,module,transistor,diodes,capacitor,resistor etc

Package : SOP-16

Factory Pack : Reel

Original IC Electronic Components 74HC585D Dual AND OR Gate CMOS Device

74HC58 Dual AND-OR gate

FEATURES

• Output capability: standard

• ICC category: SSI

GENERAL DESCRIPTION

The 74HC58 is a high-speed Si-gate CMOS device and is pin compatible with low power Schottky TTL (LSTTL). It is specified in compliance with JEDEC standard no. 7A.

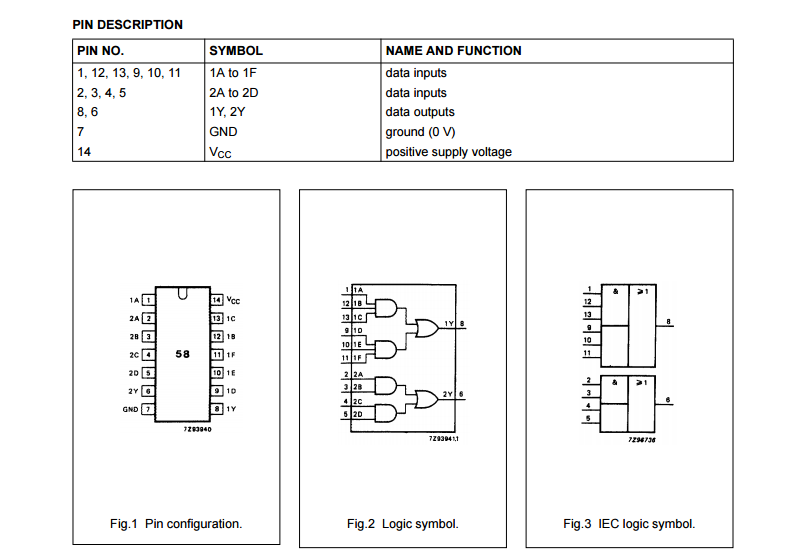

The “58” provides two sections of AND-OR gates. One section contains a 2-wide, 3-input (1A to 1F) AND-OR gate and the second section contains a 2-wide, 2-input (2A to 2D) AND-OR gate.

QUICK REFERENCE DATA

| SYMBOL | PARAMETER | CONDITIONS | TYPICAL HC | UNIT |

| tPHL/ tPLH | propagation delay 1n to 1Y 2n to 2Y | CL = 15 pF; VCC = 5 V | 11 9 | ns ns |

| CI | input capacitance | 3.5 | pF | |

| CPD | power dissipation capacitance per gate | notes 1 and 2 | 18 | pF |

Notes

1. CPD is used to determine the dynamic power dissipation (PD in µW): PD = CPD × VCC2 × fi + ∑ (CL × VCC2 × fo) where: fi = input frequency in MHz fo = output frequency in MHz CL = output load capacitance in pF VCC = supply voltage in V ∑ (CL × VCC2 × fo) = sum of outputs

2. For HC the condition is VI = GND to VCC

|

|

Original IC Electronic Components 74HC585D Dual AND OR Gate CMOS Device Images |